# Studying Crosstalk Trends for Signal Integrity on Interconnects using Finite Element Modeling.

Grover\*1, Dr. Gupta\*\*2

<sup>1</sup>BITS Pilani- Pilani Campus, <sup>2</sup>BITS Pilani-Pilani Campus.

- \* Electronics and Instrumentation Engineering, BITS Pilani, jaskaran.bits@gmail.com

- \*\* Electrical and Electronics Engineering Department, BITS Pilani, anug@pilani.bits-pilani.ac.in

**Abstract:** In this paper, the effect of crosstalk on 2 single level interconnects is analyzed and also the trends of crosstalk with substrate properties and geometrical dimensions are studied. Finite element method for transmission line model is used. The capacitance and inductance matrices are extracted by a Finite element method based solver as, such a solution is accurate and fast. By varying the dielectric constant of the substrate, its height, pitch-ratio and inserting grounding conductors, the minimum crosstalk model is proposed which has a 78% reduction in crosstalk on aggressor. The computational work for matrix extraction was carried in COMSOL and the graphs for crosstalk trends were made using MATLAB.

**Keywords:** Crosstalk, Interconnect, Microstrip, Signal Integrity.

#### 1. Introduction

Today, Microstrip transmission lines are gaining great attention in high speed digital design and in microwave integrated circuit applications. With increased density of packing, line-to-line coupling of electromagnetic energy also becomes prominent. This is known as crosstalk [5], [6]. This coupling is modeled in terms of mutual capacitance and inductance respectively. Thus greater the number of transmission lines, greater will be the size of the capacitance and inductance matrices. For a preliminary first-order analysis, we restrict the configuration to that of 2 interconnects where each matrix size is 2 x 2. The first interconnect will be called the Aggressor and the second will be called the Victim. (Refer to Figure 2.1) The aggressor is given a ramp input 1 V in magnitude with a rise time of 100 ps and the worst-case near & far end crosstalk is evaluated using basic transmission line theory (references [5], [6]). Then by varying different parameters such as dielectric-constant, height of substrate, pitch ratio and insertion of ground, a model with 78 percent reduction in crosstalk is arrived at. The rest of the paper is organized as follows:

Section 2 describes about the transmission line model, geometry and mathematical equations. In Section 3, we detail about the use of COMSOL and the steps involved in extracting impedance matrices. In Section 4, we talk about the results and discussions relating to parameters that influence crosstalk variation. We consider the grounding case in Section 5. Finally in Section 6, we present the Conclusion followed by References.

## 2. Description of Transmission Line Model using Finite Element Method.

#### 2.1 Transmission Line modeling

From reference [7], it is known that for sufficiently long transmission lines (length in centimeters) and for comparable signal risetime and time of flight cases, the interconnection lines cannot be treated as lumped models. This is because inductance matrix also becomes important and hence transmission line modeling is needed. This modeling is done using Finite Element method based COMSOL because of its accuracy and consonance with other methods such as Method of Moments and Green's Function method as has been demonstrated in [1] and [2]. The mesh-element size was equal to 5e-6 for accurate solution of impedance matrices and number of elements in the subdomains was 2860.

#### 2.2 Geometry Description

Refer to Figure 2.1 for better understanding of the geometry. The configuration chosen is simple. It consists of 2 microstrips or transmission lines each of thickness (height) 't'  $\mu$ m each and width 'w'  $\mu$ m each. They are separated by a distance 's'  $\mu$ m and both of them are sitting on the top of a dielectric with width 'W'  $\mu$ m and height 'H'  $\mu$ m. The entire arrangement is enclosed inside a big box to ensure shielding. The width of the box is 'A'  $\mu$ m

and height is 'B µm'. The shielding box is supposed to be big enough to make the influence of the terminating conditions negligible as otherwise we require a very large mesh which will be computationally impossible. The dimensions which are usually in micrometers are specified in Table 2.1.

Figure 2.1: Geometry of the Transmission Lines.

Table 2.1

| Label           | Value  |

|-----------------|--------|

| 1) A (Fixed)    | 200 μm |

| 2) B (Fixed)    | 80 μm  |

| 3) W (Fixed)    | 80 μm  |

| 4) H (Variable) | 10 μm  |

| 5) w (Variable) | 5 μm   |

| 6) s (Variable) | 5 μm   |

#### 2.3 Equations and Formulae

The geometry presented above consists of a 2 x 2 Capacitance matrix and a 2 x 2 Inductance matrix. The diagonal elements represent self-impedances whereas off-diagonal values represent mutual capacitance and inductance respectively. The capacitance matrix is computed using the *rlcmatrix* command in Script. The underlying theory is as follows: each conductor is given a 1 Volt potential at a time with the other one grounded. The computed charge is indicative of capacitance.

$$\begin{bmatrix} Q1\\Q2 \end{bmatrix} = \begin{bmatrix} C11V1 + C12V2\\C21V1 + C22V2 \end{bmatrix}$$

The per-unit length capacitance matrix is therefore:

Where  $C_{12}$  and  $C_{21}$  are equal and both negative. The units are pF/cm. For the inductance matrix, we need to set each dielectric constant to 1, compute the capacitance matrix and then deduce the inductance matrix using the formula below:

$$[L] = (\mu_0 \, \epsilon_0) \, [C^*]^{-1}$$

Where  $C^*$  is the capacitance matrix with all dielectric constants set to 1. Thus the inductance matrix will change only with changes in geometry and spacing. To save computation while sweeping  $\varepsilon_r$  of the substrate, the L matrix will remain same and hence, not evaluated. The resultant per-unit length L matrix is as follows:

$$\begin{bmatrix} L11 & L12 \\ L21 & L22 \end{bmatrix}$$

Where  $L_{12} = L_{21}$  and units are nH/cm.

Having obtained the capacitance and inductance matrices, we turn to crosstalk. As mentioned before, the aggressor is given a 1V ramp input with a rise time of 100 ps. The far-end crosstalk is evaluated on the victim and near end on aggressor.

The time domain and frequency domain expressions for the crosstalk induced voltage can be found in any of the references ([3] and [5]). In our case we have considered that interconnects have some finite source as well as load impedance (each equal to the characteristic impedance of the line which is  $50\Omega$ ). We monitor the maximum value of crosstalk at the near end of the aggressor or the far end of the victim. Thus we have for the near end of the aggressor

$$A(near) = \frac{V(input)}{4} \left( \frac{Lm}{L} + \frac{Cm}{C} \right)$$

and for the victim's far end we have:

$$B(far) = -\frac{V(input) * X * \sqrt{LC}}{2 * Tr} \; \left(\frac{Lm}{L} - \frac{Cm}{C}\right)$$

Where Tr is the rise time of the input signal, Lm and Cm are the mutual impedances given by the off-diagonal elements of the matrices. For our case, the input signal has a rise time of 100ps.

#### 3. Use of COMSOL Multiphysics

COMSOL Multiphysics was used to extract perunit length line parameters which include capacitance and inductance matrices. We used the standard 2D AC/DC Module and specified 'Electrostatics' as the mode. The model is simple as can be seen from Figure 2.1. After constructing the model we specify the initial and boundary conditions. For the outer boundary condition we specify (V = 0) which is attributed to the ground or shield. We use continuity boundary condition between the conductors and between the left and right grounds. The conductors are specified as ports to calculate self and mutual capacitances depending on the setting i.e. assign Port 1 to the first conductor and Port 2 to the second. Next we specify the subdomain properties. Firstly, change the thickness of interconnects to 10 cm each and their material to copper. Next, change the dielectric constant of the substrate material to 10. To compute the capacitance matrix, we need to do an initial meshing and one-time refinement would suffice. For our purpose, we specified the mesh size as 5e-6 for all subdomains. Next we export the model to script and using the rlcmatrix command we extract the per-unit impedance matrices. For parametric analysis, we modify various properties inside the script model file. We consider three parameters namely 1) Dielectric constant of the substrate 2) Thickness of the Substrate and 3) Pitch Ratio i.e. s/w ratio.

#### 4. Results and Discussions:

It is assumed that both the victim and aggressor lines are terminated by load resistances whose value is equal to the characteristic impedance of the line which is  $50\Omega$ . Similarly, the source impedance of both lines is also the same as characteristic impedance  $50\Omega$ . The trends of crosstalk voltage with different parameters are observed. Each parameter is varied one at a time. Firstly, the dielectric constant is considered, then Substrate thickness and finally, the Pitch-Ratio.

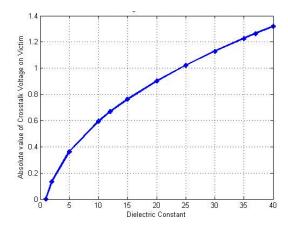

### 4.1 Variation of Dielectric Constant of Substrate:

The dielectric constant is varied for pitch ratio=1 and for substrate thickness =10  $\mu$ m. We have varied it in regular steps of 3 from 1 to 40. The maximum crosstalk is plotted v/s dielectric constant. It is found that for a given pitch-ratio and substrate thickness, the absolute value of the maximum crosstalk on the victim increases with increasing dielectric constant. It is equal to 0.6 V for a dielectric constant of 10 (alumina) and

nearly 1.3V for dielectric constant of 40. This indicates a square-root dependence of crosstalk on dielectric constant. Thus we would prefer to have low-k materials as substrates. This relation can be seen from the graph in Figure 4.1

**Figure 4.1.**Variation of maximum crosstalk with dielectric constant of substrate (near end of aggressor).

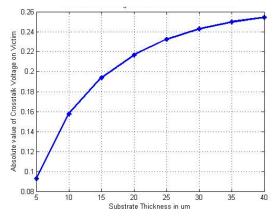

#### 3.2 Variation of the Substrate Thickness

Once again, the parameters are varied one at a time. Thus the thickness of substrate is varied for dielectric constant=10(alumina) and for pitchratio = 1. We have varied it in regular steps of  $5\mu\text{m}$  from  $5\mu\text{m}$  to  $40\mu\text{m}$ . The maximum crosstalk is plotted v/s dielectric constant. It is found that for a given dielectric constant and pitch-ratio, the maximum crosstalk increases with increasing substrate thickness. This is due to the reduced effect of shielding from ground with increasing distance from ground plane. This relation can be seen from the graph in Figure 4.2:

**Figure 4.2.** Variation of maximum crosstalk with thickness of substrate.

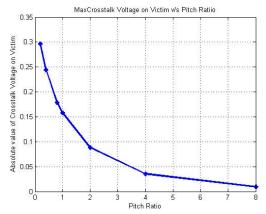

#### 4.3 Variation of the Pitch-Ratio

Finally, we vary the pitch-ratio. This represents the separation between interconnects relative to their width. It is obvious that increasing the spacing alone will decrease the crosstalk substantially. However, the same is not true for variation in pitch-ratio. With increasing pitch ratio, the crosstalk does not fall quickly and rather takes time to reach small values. This can be seen in the graph in Figure 4.3. Here we varied the ratio in steps of 1 each from 0.25 till 8. The thickness of substrate is 10  $\mu m$  and dielectric constant is 10 corresponding to alumina. Observe that for pitch-ratio=8, the crosstalk induced voltage has nearly become zero.

**Figure 4.3.** Variation of maximum crosstalk with Pitch Ratio (near end of aggressor).

#### 5. Case Study:

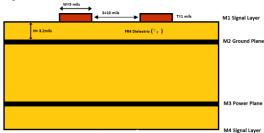

The figure below shows the stack-up of a standard four-layer motherboard. The ground plane M2 is close to the transmission lines. This ensures strong coupling of the transmission lines to the ground plane and less to the nearby signals.

Figure 5.1. Stackup of 4 layer PCB.

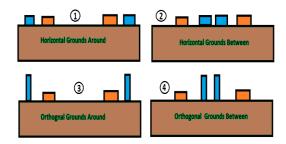

Further, we did simulations to find out the configuration in which insertion of 2 more ground planes will lead to minimum crosstalk.

- 1) Horizontal Grounds Between the lines.

- 2) Horizontal Grounds Around the lines.

- 3) Orthogonal Grounds Between the lines.

- 4) Orthogonal Grounds Around the lines.

Refer to Figure 5.2 for all corresponding configurations.

Figure 5.2. Configurations for ground insertion

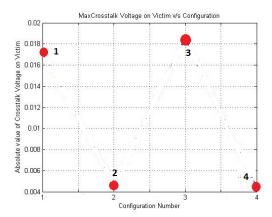

Our results indicate that inserting orthogonal grounds between the two line leads to minimum crosstalk on both aggressor and victim. From the graph of Figure 5.3, it is observed that configuration 4, which corresponds to Orthogonal Grounds between interconnects, has minimum crosstalk induced voltage.

**Figure 5.3**. Crosstalk v/s Configuration

For comparison purposes, we consider two cases Case A and Case B which have properties as listed in Table 5.1 Case A has high-dielectric constant, thick substrate and small pitch ratio. The opposite is true for case B. The maximum crosstalk voltages on the Victim and Aggressor for both cases illustrates that 50% change in each

value leads to 78.22% decrease in crosstalk on aggressor and 19% decrease on victim.

Table 5.1

| Property            | CASE A   | CASE B   |

|---------------------|----------|----------|

| Dielectric Constant | 30       | 15       |

| Substrate Thickness | 30 µm    | 15 μm    |

| Pitch Ratio         | 3        | 6        |

| Crosstalk Aggressor | 0.135 V  | 0.0294 V |

| Crosstalk Victim    | -0.377 V | -0.306 V |

#### 6. Conclusions:

In this paper, we have considered a simple configuration of two interconnects which sit on the top of a dielectric. We used Finite-element method based solver COMSOL for transmission line modeling as this method is accurate and close to values predicted by other computational methods as mentioned in [1] and [2]. After calculating the impedance matrices, we use them to deduce crosstalk. We analyze the variation of crosstalk with dielectric constant, substrate thickness and pitch ratio. We can conclude that a low-k and a thin substrate are preferred. Further, we must keep the pitch ratio high. Insertion of ground planes reduces crosstalk but has several other integrity related and routing limitations. These ideas if kept in mind can help minimize crosstalk.

#### 6. References

- SM Musa, NMO Sadiku,"Analysis of Multiconductor Quasi-TEM Transmission Lines and Multimode waveguides", Excerpt from the Proceedings of the COMSOL Conference 2010, Boston

- SM Musa, NMO Sadiku, "Finite Element Analysis of Multilayer Transmission Lines for High-Speed Digital Interconnects", Excerpt from the Proceedings of the COMSOL Conference 2010, Boston

- D.Gao, A. T. Yang, and S. M. Kang, "Modeling and simulation of interconnection delays and crosstalk in highspeed integrated circuits," IEEE Trans. Circuits Syst., vol. 37, pp. 1-9, Mar. 1990.

- Hang You, Mani Soma," Crosstalk and Transient Analyses of High-speed Interconnects and Packages", IEEE Journal of Solid State Circuits, Volume 26,No.3 pp 319-329 (March 1991)

- 5. Ashok Goel, "High Speed VLSI Interconnection: Modeling, Analysis and Simulation", Wiley series in Microwave and Optical Engineering.

- Stephen Hall, Garrett Hall, James McCall

"High Speed Digital System Design: A

handbook of interconnect theory and Design

Practices", A Wiley Interscience

Publication.

- 7. Sung Kang, Yusuf Leblebici, "CMOS Digital Integrated Circuits, Analysis and Design", Tata McGraw Hill Publishing Company Limited.